High-speed and low-power asynchronous Network-on-Chip system based multiple-valued current-mode logic

High-speed and low-power asynchronous Network-on-Chip system based multiple-valued current-mode logic

- Features and Uniqueness

-

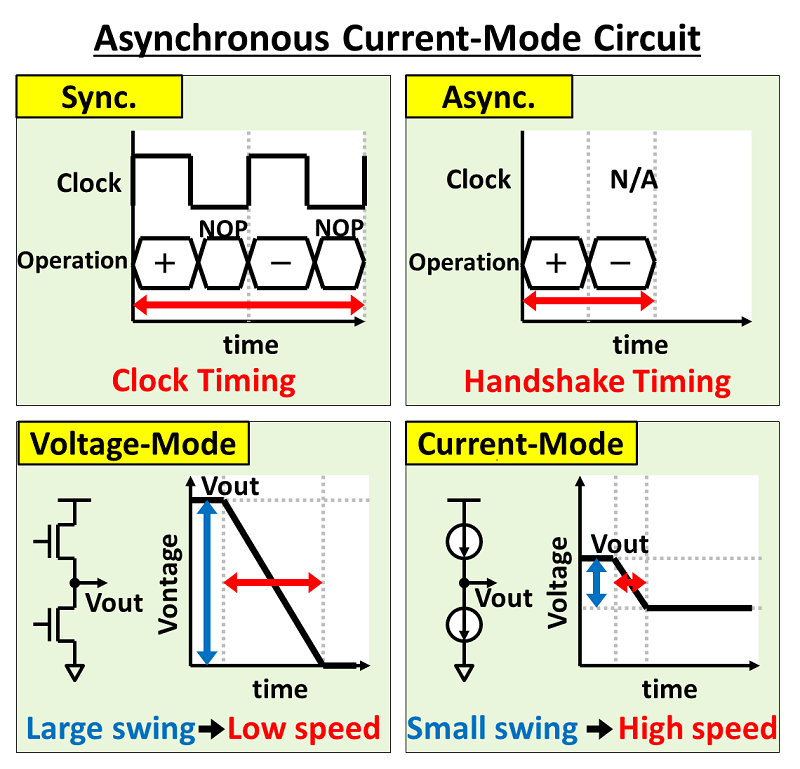

Global intra-chip interconnection complexity not only limits the clock frequency, but causes clock-skew problems in synchronous system. Asynchronous control-based circuit design, where timing is managed locally, is one of the possible approaches to solve the above serious interconnection problem because the asynchronous design has many features which are low power dissipation, high speed and robustness. However, communication-steps overhead caused by handshaking much would generally affect the cycle time.

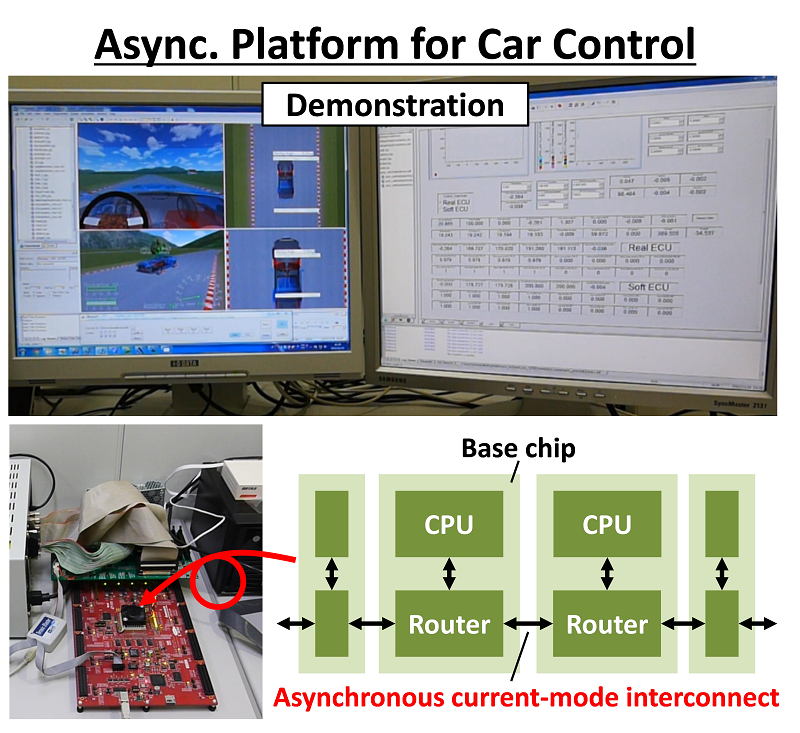

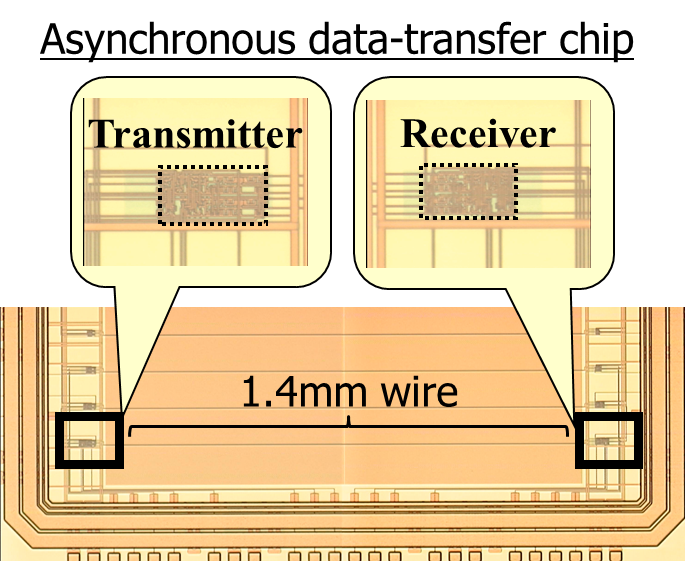

In our approach, a high-speed asynchronous data-transfer scheme is proposed based on multiple-valued encoding and current-mode circuits. The multiple-valued encoding enables to improve communication protocol essentially. Moreover, the current-mode circuits which has high-driving capability makes it possible to perform high-speed intra- and inter-chip network. By using this method, we expect that we can conduct effective collaborative research in high-speed and low-power communication LSIs such as a many-core LSI and a multi-module NoC. - Keywords

Medical

Medical

Life Sciences

Life Sciences

Environment

Environment

Nanotechnology / Materials

Nanotechnology / Materials

Energy

Energy

Manufacturing Technology

Manufacturing Technology

Social Infrastructure

Social Infrastructure

Frontier

Frontier

Human and social sciences

Human and social sciences